## DEPARTMENT OF ELECTRONICS AND COMMUNICATION DSP/VHDL LABORATORY MANUAL (ECE-417)

ANIL NEERUKONDA INSTITUTE OF TECHNOLOGY & SCIENCES (Affiliated to AU, Approved by AICTE &Accredited by NBA) Sangivalasa-531162, Bheemunipatnam Mandal, Visakhapatnam Dt. Phone: 08933- 225084,226395

## Vision of ANITS

ANITS envisions to emerge as a world-class technical institution whose products represent a good blend of technological excellence and the best of human values.

#### Mission of ANITS

To train young men and women into competent and confident engineers with excellent communicational skills, to face the challenges of future technology changes, by imparting holistic technical education using the best of infrastructure, outstanding technical and teaching expertise and an exemplary work culture, besides molding them into good citizens.

#### Vision of the department

To become a centre of excellence in education & research and produce high quality engineers in the field of Electronics & Communication Engineering to face the challenges of future technological changes.

#### Mission of the department

The Department aims to bring out competent young Electronics & Communication Engineers by achieving excellence in imparting technical skills, soft skills and the right attitude for continuous learning.

#### **Course Outcomes:**

| C407.1 | Model combinational and sequential digital circuits using VHDL in behavioral, structural, and dataflow models.                                                       |

|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C407.2 | Develop test benches to simulate combinational and sequential circuits, perform functional and timing verifications of digital circuits.                             |

| C407.3 | Design the digital filter circuits for generating desired signal wave shapes (non sinusoidal) for different applications like digital signal processing using MATLAB |

| C407.4 | Analyze the system in Time domain and Frequency domain through its respective tools using MATLAB.                                                                    |

#### **Program Educational Objective (PEOs)**

| PEO1 | To prepare graduates for successful career in Electronics industry, R&D organizations and/or IT |

|------|-------------------------------------------------------------------------------------------------|

|      | industry by providing technical competency in the field of Electronics & Communication          |

|      | Engineering.                                                                                    |

| PEO2 | To prepare graduates with good scientific and engineering proficiency to analyze and solve      |  |

|------|-------------------------------------------------------------------------------------------------|--|

|      | electronics engineering problems.                                                               |  |

| PEO3 | To inculcate in students professionalism, leadership qualities, communication skills and ethics |  |

|      | needed for a successful professional career.                                                    |  |

| PEO4 | To provide strong fundamental knowledge in students to pursue higher education and continue     |  |

|      | professional development in core engineering and other fields.                                  |  |

## Program Outcomes (POs): At the end of the program, the student will have

| Prog        | ram Outcomes (POS): At the end of the program, the student will have                           |  |

|-------------|------------------------------------------------------------------------------------------------|--|

| <b>PO 1</b> | An ability to apply knowledge of mathematics, science and engineering with adequate            |  |

|             | computer knowledge to electronics & communication engineering problems.                        |  |

| <b>PO 2</b> | An ability to analyze complex engineering problems through the knowledge gained in core        |  |

|             | electronics engineering and interdisciplinary subjects appropriate to their degree program.    |  |

| <b>PO 3</b> | An ability to design, implement and test electronics based system.                             |  |

| <b>PO 4</b> | An ability to design and conduct scientific and engineering experiments, as well as to         |  |

|             | analyze and interpret data.                                                                    |  |

| <b>PO 5</b> | An ability to use modern engineering techniques, simulation tools and skills to solve          |  |

|             | engineering problems.                                                                          |  |

| <b>PO 6</b> | An ability to apply reasoning in professional engineering practice to assess societal, safety, |  |

|             | health and cultural issues.                                                                    |  |

| <b>PO 7</b> | An ability to understand the impact of professional engineering solutions in societal and      |  |

|             | environmental contexts.                                                                        |  |

| <b>PO 8</b> | An ability to develop skills for employability/ entrepreneurship and to understand             |  |

|             | professional and ethical responsibilities.                                                     |  |

| <b>PO 9</b> | An ability to function effectively as an individual on multi-disciplinary tasks.               |  |

| PO 10       | An ability to convey technical material through oral presentation and interaction with         |  |

|             | audience, formal written papers /reports which satisfy accepted standards for writing style.   |  |

| PO 11       | An ability to succeed in university and competitive examinations to pursue higher studies.     |  |

| PO 12       | 2 An ability to recognize the need for and engage in life-long learning process.               |  |

| Prog        | ram Specific Outcomes (PSOs)                                                                   |  |

| The I       | Electronics and Communication Engineering graduate shall have                                  |  |

| PSO1        | Competency in the application of circuit analysis and design.                                  |  |

| PSO2        | The ability to apply knowledge of physics / chemistry / mathematics to electronic circuits.    |  |

| PSO3        | The ability to apply the knowledge of computer programming, analog & digital electronics       |  |

|             |                                                                                                |  |

|      | microprocessors, etc and associated software to design and test VLSI/ communication systems.         |  |

|------|------------------------------------------------------------------------------------------------------|--|

| PSO4 | The ability to pursue higher studies either in India or abroad in specializations like communication |  |

|      | systems, VLSI, embedded systems, signal processing, image processing, RADAR & Microwave              |  |

|      | engineering, etc and also lead a successful career with professional ethics.                         |  |

## LABORATORY MANUAL FOR THE COURSE DIGITAL SIGNAL PROCESSING LABORATORY

(ECE-417)

Lab In-charge:

Mr.A.SivaKumar Asst. Professor Dept. of ECE Dr.K.Murali Krishna Prof.&HOD Dept. of ECE

ANIL NEERUKONDA INSTITUTE OF TECHNOLOGY & SCIENCES (Affiliated to Andhra University) Sangivalasa-531162, Bheemunipatnam Mandal, Visakhapatnam Dt. Phone: 08933- 225084,226395

## INDEX

## LIST OF EXPERIMENTS

## CYCLE - I: SIGNAL PROCESSING WITH MATLAB

- 1. GENERATION OF DISCRETE-TIME SEQUENCES

- 2. IMPLEMENTATION OF DISCRETE-TIME SYSTEMS

- 3. FREQUENCY ANALYSIS OF DISCRETE-TIME SEQUENCES

- 4. FREQUENCY ANALYSIS OF DISCRETE-TIME SYSTEMS

- 5. INFINITE IMPULSE RESPONSE FILTER DESIGN

- 6. FINITE IMPULSE RESPONSE FILTER DESIGN

- 7. GENERATION OF ECG SIGNAL(ADDITIONAL EXPERIMENT)

## **CYCLE – II: VHDL EXPERIMENTS**

INTRODUCTION TO VHDL

- 1. LOGIC GATES

- 2. HALF ADDER & FULL ADDER

- 3. MULTIPLEXER AND DEMULTIPLEXER

- a. 2x1 MUX

- b. 4x1MUX

- c. 8x1 MUX

- d. 1x8 DEMUX

- 4. FLIP-FLOPS

- a. SR Flip-Flop

- b. D Flip-Flop

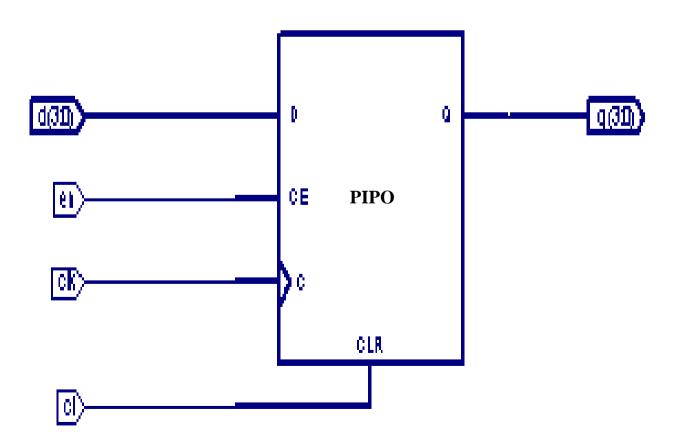

- 5. UP/DOWN COUNTER AND SHIFT REGISTERS

- a. UP/DOWN COUNTER

- b. SISO & SIPO Shift Register

- c. PISO & PIPO Shift Register.

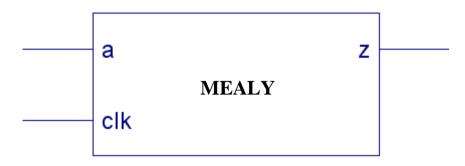

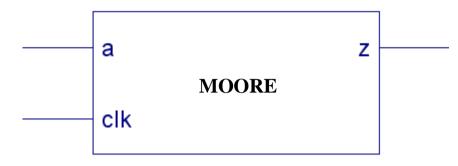

- 6. FINITE STATE MACHINES

- a. MELAY MACHINES

- b. MOORE MACHINES

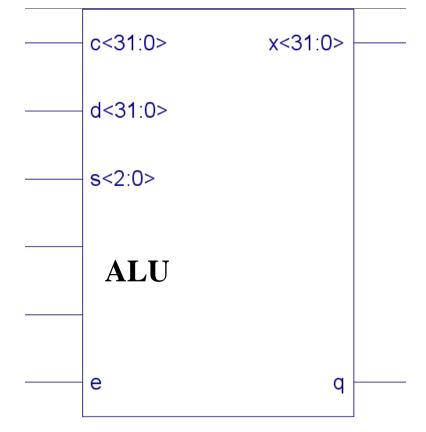

- 7. ARITHMETIC LOGIC UNIT( ADDITIONAL EXPERIMENT)

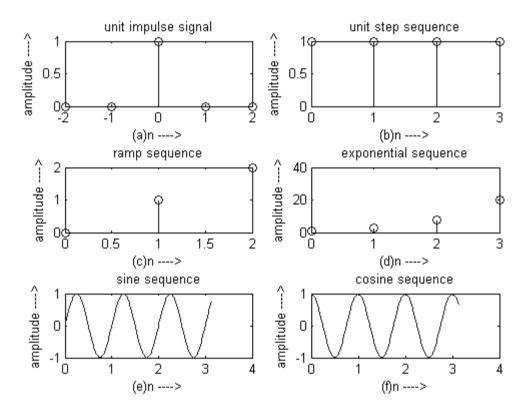

#### **PROGRAM-1 GENERATION OF DISCRETE-TIME SEQUENCES**

AIM: To generate the discrete time sequences of

- (a) Unit impulse sequence

- (b) Unit step sequence

- (c) Ramp sequence

- (d) Exponential sequence

- (e) Sinusoidal sequence

- (f) Cosine sequence.

## APPARATUS: MATLAB Version 7.8 (R2009a)

| PROGRAM:                                 |                                                |  |

|------------------------------------------|------------------------------------------------|--|

| %PROGRAM for the generation of unit      | %PROGRAM for the generation of ramp            |  |

| impulse signal                           | sequence                                       |  |

| clc ;                                    | n=input('enter the length of ramp sequence '); |  |

| clear all ;                              | t=0:n-1;                                       |  |

| close all ;                              | subplot(3,2,3);                                |  |

| t=-2:1:2 ;                               | stem(t,t);                                     |  |

| y=[zeros(1,2),ones(1,1),zeros(1,2)];     | ylabel('amplitude>');                          |  |

| subplot(3,2,1);                          | xlabel('(c)n>');                               |  |

| stem(t,y);                               | title(' ramp sequence ');                      |  |

| ylabel('amplitude>');                    | %PROGRAM for the generation of                 |  |

| xlabel('(a)n>');                         | exponential sequence                           |  |

| title(' unit impulse signal ');          | n=input('enter the length of exponential       |  |

| %PROGRAM for the generation of unit step | sequence');                                    |  |

| sequence [u(n)-u(n-N)]                   | t=0:n;                                         |  |

| n=input('enter the N value ');           | a=input('enter the value of a ');              |  |

| t=0:1:n-1;                               | y=exp(a*t);                                    |  |

| y=ones(1,n);                             | subplot(3,2,4);                                |  |

| subplot(3,2,2);                          | stem(t,y);                                     |  |

| stem(t,y);                               | ylabel('amplitude>');                          |  |

| ylabel('amplitude>');                    | xlabel('(d)n>');                               |  |

| xlabel('(b)n>');                         | title(' exponential sequence ');               |  |

| title(' unit step sequence ');           |                                                |  |

|                                          |                                                |  |

| %PROGRAM for the generation of sine      | %PROGRAM for the generation of cosine          |  |

| sequence                                 | sequence                                       |  |

| t=0:0.01:pi;              | t=0:0.01:pi ;               |

|---------------------------|-----------------------------|

| y=sin(2*pi*t);            | y=cos(2*pi*t);              |

| subplot(3,2,5);           | subplot(3,2,6);             |

| plot(t,y);                | plot(t,y);                  |

| ylabel('amplitude>');     | ylabel('amplitude>');       |

| xlabel('(e)n>');          | xlabel('(f)n>');            |

| title(' sine sequence '); | title(' cosine sequence '); |

|                           |                             |

|                           |                             |

## **MODEL GRAPHS**:

## **RUN:**

| Enter the value of N                     | : | 4 |

|------------------------------------------|---|---|

| Enter the length of ramp sequence        | : | 3 |

| Enter the length of exponential sequence | : | 3 |

| Enter the value of 'a'                   | : | 1 |

**RESULT:-** Thus the generation of discrete-time sequences of unit impulse, unit step, ramp, exponential, sinusoidal and cosine sequence is simulated using MATLAB.

#### **VIVA QUESTIONS:**

- 1. Define unit sample(impulse) sequence.

- 2. Define unit step sequence.

- 3. Define discrete-time system.

- 4. Distinguish the terms 'discrete' and 'digital' w.r.t DSP.

- 5. Define sampling theorem.

## **ANSWERS:**

1. The unit impulse sequence is denoted as  $\delta(n)$  and is defined as

$\delta(n) = 1$  for n = 0

$\delta(n) = 0$  for  $n \neq 0$ .

2. The unit step sequence is denoted as u(n) and is defined as

$$\begin{split} u(n) &= 1 \ \text{for} \ n \geq 0 \\ u(n) &= 0 \ \text{for} \ n < 0. \end{split}$$

- A discrete-time system is a device or algorithm that operates on a discrete-time input Signal x(n), according to some well-defined rule, to produce another discrete-time signal y(n) called the output signal.

- 4. Discrete may have the various amplitudes at respective interval but the digital signal should have either zero or one.

- 5. The sampling theorem states that perfect reconstruction of a signal is possible when the sampling frequency is greater than twice the maximum frequency of the signal being sampled, or equivalently, when the frequency (half the sample rate) exceeds the highest frequency of the signal being sampled. If lower sampling rates are used, the original signal's information may not be completely recoverable from the sampled signal. For example, if a signal has an upper band limit of 100 Hz, a sampling frequency greater than 200 Hz will avoid aliasing and allow theoretically perfect reconstruction.

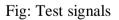

## PROGRAM 2 IMPLEMENTATION OF DISCRETE-TIME SYSTEMS

**AIM:** To find the impulse response of a system with the transfer function y(n)+1/2y(n-1)+1/3y(n-2)=x(n)

APPARATUS: MATLAB Version 7.8 (R2009a)

## PROGRAM: IMPULSE RESPONSE OF SYSTEM FOR GIVEN TRANSFER FUNCTION

y(n)+1/2y(n-1)+1/3y(n-2)=x(n)

|                                | title('impulse response h(n)'); |

|--------------------------------|---------------------------------|

| clc;                           | x=[1,2];                        |

| b=[1];                         | y=conv(h,x);                    |

| a=[1;1/2;1/3];                 | disp('output y(n)');            |

| h=impz(a,b,4);                 | disp(y);                        |

| disp('impulse response h(n)'); | n2=0:1:length(y)-1;             |

| disp(h);                       | subplot(3,2,2);                 |

| n1=0:1:length(h)-1;            | stem(n2,y);                     |

| subplot(3,2,1);                | xlabel('n2');                   |

| stem(n1,h);                    | ylabel('amplitude');            |

| <pre>xlabel('n1');</pre>       | title('outputy(n)');            |

| ylabel('x(n)');                |                                 |

|                                |                                 |

#### **MODEL GRAPHS:**

**RESULT**: Thus the generation of impulse sequence for given difference equation is simulated using MATLAB.

## VIVA

- 1. What is meant by impulse response of a system?

- 2. How to generate impulses using MATLAB?

- 3. What is the role of convolution in finding the impulse response of a system?

- 4. What is an LTI system?

## **ANSWERS:**

- 1. In signal processing, the **impulse response**, or **impulse response function (IRF)**, of a dynamic system is its output when presented with a brief input signal, called an impulse.

- 2. >> freq = fft(impulse Train, Len); >> stem([(0:Len-1)/(Len\*Ts)], abs(freq)).

- 3. Convolution is a very powerful technique that can be used to calculate the zero state response (i.e., the response to an input when the system has zero initial conditions) of a system to an arbitrary input by using the impulse response of a system.

- 4. Linear time-invariant system theory, commonly known as LTI system theory, comes from applied mathematics and has direct applications in NMR spectroscopy, seismology, circuits, signal processing, control theory, and other technical areas. It investigates the response of a linear and time-invariant system to an arbitrary input signal. Trajectories of these systems are commonly measured and tracked as they move through time (e.g., an acoustic waveform).

#### **PROGRAM-3** FREQUENCY ANALYSIS OF DISCRETE-TIME SEQUENCES

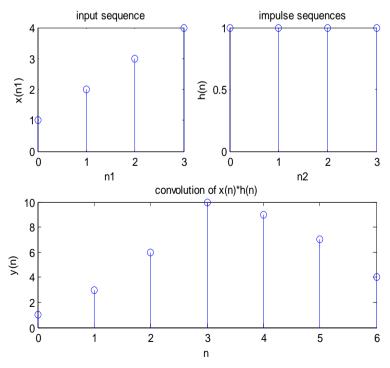

## A) LINEAR CONVOLUTION

## **B) CIRCULAR CONVOLUTION**

## AIM: To plot linear convolution of two sequences using FFT.

APPARATUS: MATLAB Version 7.8 (R2009a)

## **PROGRAM:**

| Linear convolution         |                                               |  |

|----------------------------|-----------------------------------------------|--|

| x=[1,2,3,4];               | xlabel('n2');                                 |  |

| N1=length(x);              | ylabel('h(n)');                               |  |

| n1=0:1:N1-1;               | title('impulse sequences');                   |  |

| subplot(2,2,1),stem(n1,x); | y=conv(x,h);                                  |  |

| xlabel('n1');              | n=0:1:length(y)-1;                            |  |

| ylabel('x(n1)');           | <pre>subplot(2,1,2),stem(n,y);</pre>          |  |

| title('input sequence');   | xlabel('n');                                  |  |

| h=[1,1,1,1];               | ylabel('y(n)');                               |  |

| N2=length(h);              | <pre>title('convolution of x(n)*h(n)');</pre> |  |

| n2=0:1:N2-1;               |                                               |  |

| subplot(2,2,2),stem(n2,h); |                                               |  |

## **MODEL GRAPHS:**

**RESULT**: Thus the linear convolution of two given sequences is simulated using MATLAB.

## AIM: To plot circular convolution of two sequences using FFT.

APPARATUS: MATLAB Version 7.8 (R2009a)

## **METHOD:**

Let  $X_1(K) = FFTx_1(n)$ ;  $X2(K) = FFTx_2(n)$ .

1)Take N point FFTof x1(n) & x2(n)

2) X3(K)=X1(K) \* X2(K);

3) IFFT (X3(k))=x3(n); x3(n) is the convolution of x1(n) & x2(n).

#### **PROGRAM:**

| <pre>x1= input('enter the first sequence');</pre> | N=0:1:N-1;           |

|---------------------------------------------------|----------------------|

| x2= input('enter the second sequence');           | subplot(1,1,1);      |

| N=max(length(x1),length(x2));                     | stem(N,x3);          |

| X1= fft(x1,N);                                    | xlabel('time');      |

| X2=fft(x2,N);                                     | ylabel('magnitude'); |

| X3= X1.*X2;                                       |                      |

| x3 = ifft(X3,N);                                  |                      |

| disp('circular convolution');                     |                      |

| disp(x3);                                         |                      |

**RESULT**: Thus the circular convolution of two given sequences using DFT and IDFT is simulated in MATLAB.

#### **VIVA QUESTIONS**:

- 1. Why should we go for frequency analysis instead of time analysis?

- 2. Define i) linear ii) circular convolution.

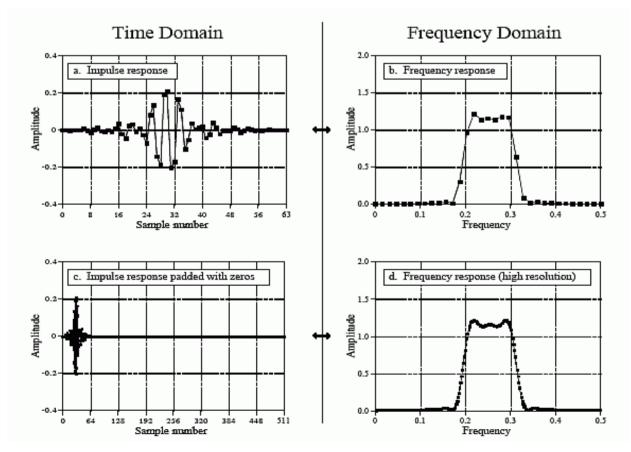

- 3. What is meant by zero padding? Why do we use it?

- 4. Distinguish between linear and circular convolution.

- 5. Where is DFT used?

#### **ANSWERS:**

- 1. In signal processing time–frequency analysis comprises those techniques that study a signal in both the time and frequency domains *simultaneously*, using various time–frequency representations. Rather than viewing a 1-dimensional signal (a function, real or complex-valued, whose domain is the real line) and some transform (another function whose domain is the real line, obtained from the original via some transform), time–frequency analysis studies a two-dimensional signal a function whose domain is the two-dimensional real plane, obtained from the signal via a time–frequency transform.

- 2. A) linear Convolution is an integral concatenation of two signals. It has many applications in numerous areas of signal processing. The most popular application is the determination of the output signal of a linear time-invariant system by convolving the input signal with the impulse response of the system.

B) The circular convolution, also known as cyclic convolution, of two aperiodic functions occurs when one of them is convolved in the normal way with a periodic summation of the other function.

- 3. Zero padding consists of extending a signal (or spectrum) with zeros. It maps a length N signal to a length M>N signal, but N need not divide M.

- 4. In linear convolution we convolved one signal with another signal where as in circular convolution the same convolution is done but in circular pattern ,depending upon the samples of the signal.

- 5. The Discrete Fourier Transform (DFT) is one of the most important tools in Digital Signal Processing. This chapter discusses three common ways it is used. First, the DFT can calculate a signal's *frequency spectrum*. This is a direct examination of information encoded in the frequency, phase, and amplitude of the component sinusoids. For example, human speech and hearing use signals with this type of encoding. Second, the DFT can find a system's frequency response from the system's impulse response, and vice versa.

#### PROGRAM 4 FREQUENCY ANALYSIS OF DISCRETE-TIME SYSTEMS

AIM: To find the N-point DFT of a given sequence using Fast Fourier Transform(FFT).

APPARATUS: MATLAB Version 7.8 (R2009a)

## **PROGRAM:**

## % N POINT FFT

| Clc;                                     | xlabel('length');                   |

|------------------------------------------|-------------------------------------|

| x1=input('enter the sequence');          | ylabel('magnitude of DFT of x(k)'); |

| n=input('enter the length');             | title('magnitude spectrum');        |

| m=fft(x1,n);                             | an = angle('m');                    |

| y = abs(m);                              | subplot(2,2,2);                     |

| disp('N-Point DFT of a given sequence'); | stem(N,an);                         |

| disp(y);                                 | ylabel('phase of DFT of x(n)');     |

| N = 0:1:n-1;                             | xlabel('length');                   |

| subplot(2,2,1);                          | title('phase spectrum');            |

| stem(N,y);                               |                                     |

|                                          |                                     |

## **MODEL GRAPHS:**

#### **VIVA QUESTIONS:**

- 1. What is need of discrete Fourier Transform ?

- 2. What is the difference between DFT and IDFT?

- 3. What is the difference between DFT and FFT?

- 4. How to calculate output of DFT using MATLAB?

- 5. Give the defining equation for performing circular convolution using DFT.

#### **ANSWERS:**

- It transforms one function into another, which is called the *frequency domain* representation, or simply the *DFT*, of the original function (which is often a function in the time domain).

- 2) Discrete Fourier Transform (DFT) is defined as F(k), where k=0..N-1:

$$F(k) = \frac{1}{\sqrt{N}} \sum_{n=0}^{N-1} f(n) e^{-j2\pi k n/N}$$

The sequence f(n) can be calculated from F(k) using the Inverse Discrete Fourier Transform (IDFT):

$$f(n) = \frac{1}{\sqrt{N}} \sum_{k=0}^{N-1} F(k) e^{+j2\pi nk/N}$$

- 3) A DFT (Discrete Fourier Transform) is simply the name given to the Fourier Transform when it is applied to digital (discrete) rather than an analog (continuous) signal. An FFT (Fast Fourier Transform) is a faster version of the DFT that can be applied when the number of samples in the signal is a power of two. An FFT computation takes approximately N \* log2(N) operations, whereas a DFT takes approximately N^2 operations, so the FFT is significantly faster.

- 4) X = fft(x); plot(abs(X))

- 5) we can write the **circular convolution** of functions h and x as:

$$(x_N * h)[n] \stackrel{\text{def}}{=} \sum_{m=-\infty}^{\infty} h[m] \cdot x_N[n-m]$$

$$= \sum_{m=-\infty}^{\infty} \left( h[m] \cdot \sum_{k=-\infty}^{\infty} x[n-m-kN] \right).$$

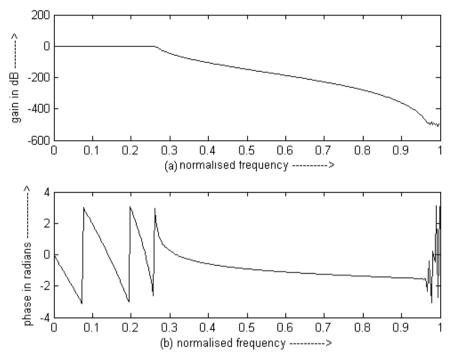

#### **PROGRAM-5 IIR FILTER DESIGN**

## AIM: To design Chebyshev type-1 IIR filters

- (a) Low pass filter.

- (b) High pass filter.

- (c) Band pass filter.

- (d) Band stop filter.

## APPARATUS: MATLAB Version 7.8 (R2009a)

#### **PROGRAM**:

## %PROGRAM for the design of Chebyshev type-1 low pass digital filter

| clc;                                      | [b,a]=cheby1(n,rp,wn);                              |

|-------------------------------------------|-----------------------------------------------------|

| close all ;                               | w=0:0.01:pi ;                                       |

| clear all ;                               | [h,om]=freqz(b,a,w);                                |

| format long                               | $m=20*\log 10(abs(h));$                             |

| rp=input('enter the passband ripple');    | an=angle(h);                                        |

| rs=input('enter the stopband ripple');    | subplot(2,1,1);                                     |

| wp=input('enter the passband frequency'); | plot(om/pi,m);                                      |

| ws=input('enter the stopband frequency'); | ylabel('gain in dB>');                              |

| fs=input('enter the sampling frequency'); | xlabel('(a) normalized frequency>');                |

| w1=2*wp/fs;                               | subplot(2,1,2);                                     |

| w2=2*ws/fs ;                              | plot(om/pi,an);                                     |

| [n,wn]=cheb1ord(w1,w2,rp,rs);             | <pre>xlabel('(b) normalized frequency&gt;') ;</pre> |

|                                           | ylabel('phase in radians>');                        |

|                                           |                                                     |

## %PROGRAM for the design of Chebyshev type-1high pass filter

| clc;                                      | fs=input('enter the sampling frequency'); |  |

|-------------------------------------------|-------------------------------------------|--|

| close all ;                               | w1=2*wp/fs;                               |  |

| clear all ;                               | w2=2*ws/fs ;                              |  |

| format long                               | [n,wn]=cheb1ord(w1,w2,rp,rs);             |  |

| rp=input('enter the passband ripple');    | [b,a]=cheby1(n,rp,wn,'high');             |  |

| rs=input('enter the stopband ripple');    | w=0:0.01/pi:pi ;                          |  |

| wp=input('enter the passband frequency'); | [h,om]=freqz(b,a,w);                      |  |

| ws=input('enter the stopband frequency'); | $m=20*\log 10(abs(h));$                   |  |

| an=angle(h);                              | subplot(2,1,2);                           |  |

| subplot(2,1,1);                      | plot(om/pi,an);                                    |

|--------------------------------------|----------------------------------------------------|

| plot(om/pi,m);                       | <pre>xlabel('(b) normalized frequency&gt;');</pre> |

| ylabel('gain in dB>');               | ylabel('phase in radians>');                       |

| xlabel('(a) normalized frequency>'); |                                                    |

|                                      | ylabel('phase in radians>');                       |

## %PROGRAM for the design of Chebyshev type-1band pass digital filter

| clc ;                                                | [b,a]=cheby1(n,rp,wn,'bandpass');                  |

|------------------------------------------------------|----------------------------------------------------|

| close all ;                                          | w=0:0.01:pi ;                                      |

| clear all ;                                          | [h,om]=freqz(b,a,w);                               |

| format long                                          | m=20*log10(abs(h));                                |

| rp=input('enter the passband ripple');               | an=angle(h);                                       |

| rs=input('enter the stopband ripple');               | subplot(2,1,1);                                    |

| wp=input('enter the passband frequency');            | plot(om/pi,m);                                     |

| ws=input('enter the stopband frequency');            | ylabel('gain in dB>');                             |

| <pre>fs=input('enter the sampling frequency');</pre> | <pre>xlabel('(a) normalized frequency&gt;');</pre> |

| w1=2*wp/fs;                                          | subplot(2,1,2);                                    |

| w2=2*ws/fs;                                          | plot(om/pi,an);                                    |

| [n]=cheb1ord(w1,w2,rp,rs);                           | <pre>xlabel('(b) normalized frequency&gt;');</pre> |

| wn=[w1,w2];                                          | ylabel('phase in radians>');                       |

|                                                      |                                                    |

## %PROGRAM for the design of Chebyshev type-1band stop digital filter

| clc;                                      | [b,a]=cheby1(n,rp,wn,'stop');                      |

|-------------------------------------------|----------------------------------------------------|

| close all ;                               | w=0:0.1/pi:pi;                                     |

| clear all ;                               | [h,om]=freqz(b,a,w);                               |

| format long                               | m=20*log10(abs(h));                                |

| rp=input('enter the passband ripple');    | an=angle(h);                                       |

| rs=input('enter the stopband ripple');    | subplot(2,1,1);                                    |

| wp=input('enter the passband frequency'); | plot(om/pi,m);                                     |

| ws=input('enter the stopband frequency'); | ylabel('gain in dB>');                             |

| fs=input('enter the sampling frequency'); | xlabel('(a) normalized frequency>');               |

| w1=2*wp/fs;                               | subplot(2,1,2);                                    |

| w2=2*ws/fs;                               | plot(om/pi,an);                                    |

| [n]=cheb1ord(w1,w2,rp,rs);                | <pre>xlabel('(b) normalized frequency&gt;');</pre> |

| wn=[w1,w2];                               | ylabel('phase in radians>')                        |

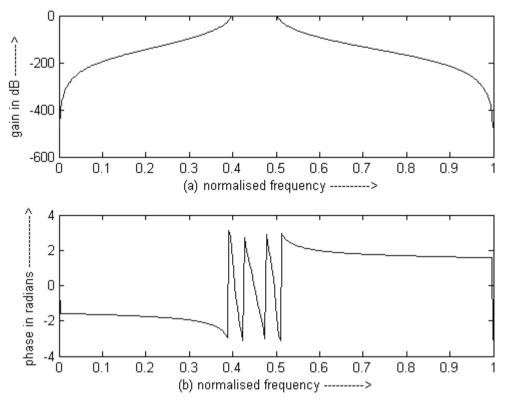

## **MODEL GRAPHS**:

Fig: Chebyshev type-1 low pass filter

#### **Parameters:**

| Enter the pass band ripple    | : 0.2   |

|-------------------------------|---------|

| Enter the stop band ripple    | : 45    |

| Enter the pass band frequency | : 1300  |

| Enter the stop band frequency | : 1500  |

| Enter the sampling frequency  | : 10000 |

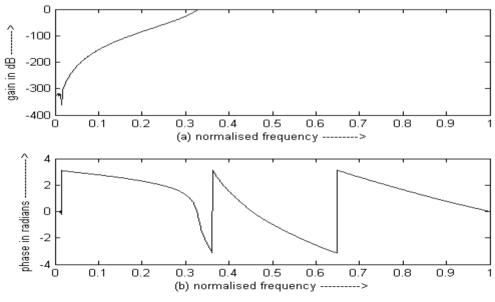

## (b) High pass filter:

Fig: Chebyshev type-1high pass filter

## **Parameters:**

| Enter the pass band ripple    | : 0.3  |

|-------------------------------|--------|

| Enter the stop band ripple    | : 60   |

| Enter the pass band frequency | : 1500 |

| Enter the stop band frequency | : 2000 |

| Enter the sampling frequency  | : 9000 |

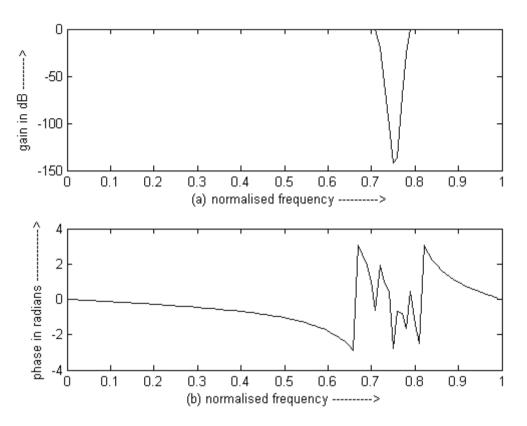

## (c) Band pass filter:

Fig: Chebyshev type-1band pass filter

## **Parameters:**

Enter the pass band ripple: 0.4Enter the stop band ripple: 35Enter the pass band frequency: 2000Enter the stop band frequency: 2500Enter the sampling frequency: 10000

Fig: Chebyshev type-1band stop filter

#### **Parameters:**

| Enter the pass band ripple    | : 0.25 |

|-------------------------------|--------|

| Enter the stop band ripple    | : 40   |

| Enter the pass band frequency | : 2500 |

| Enter the stop band frequency | : 2750 |

| Enter the sampling frequency  | : 7000 |

**RESULT**: Thus the Infinite Impulse Response(IIR) of the Chebyshev type-1 low-pass, high-pass, band pass and band reject filters is simulated in MATLAB.

## **VIVA QUESTIONS:**

- 1. Define IIR filters?

- 2. What is the transfer function of IIR filters?

- 3. What are different types of IIR filters?

- 4. Distinguish between frequency response of Chebyshev and Butterworth filters?

- 5. How to define the order of the IIR filter?

#### **ANSWERS:**

- The impulse responses of recursive filters are composed of sinusoids that exponentially decay in amplitude. In principle, this makes their impulse responses *infinitely long*. However, the amplitude eventually drops below the round-off noise of the system, and the remaining samples can be ignored. Because of this characteristic, recursive filters are also called Infinite Impulse Response or IIR filters. In comparison, filters carried out by convolution are called Finite Impulse Response or FIR filters.

- 2) Infinite impulse response (IIR) is a property of signal processing systems. Systems with this property are known as *IIR systems* or, when dealing with filter systems, as *IIR filters*. IIR systems have an impulse response function that is non-zero over an infinite length of time. This is in contrast to finite impulse response (FIR) filters, which have fixed-duration impulse responses.

- 3) IIR filters may be implemented as either analog or digital filters. In digital IIR filters, the output feedback is immediately apparent in the equations defining the output.

- 4) **Chebyshev filters** are analog or digital filters having a steeper roll-off and more passband ripple (type I) or stopband ripple (type II) than Butterworth filters. Chebyshev filters have the property that they minimize the error between the idealized and the actual filter characteristic over the range of the filter, but with ripples in the passband.

- 5) The order of a recursive filter is the *largest number of previous input or output values* required to compute the current output.

## **PROGRAM-6 FIR FILTER DESIGN**

AIM: To design Chebyshev type-1 FIR filters

- (a) Low pass filter

- (b) High pass filter

- (c) Band pass filter

- (d) Band stop filter.

#### APPARATUS: MATLAB Version 7.8 (R2009a)

#### **PROGRAM** :

# %PROGRAM for the design of FIR low pass, high pass, band pass and band stop filter using %Chebyshev window

| % low pass filter                                  |

|----------------------------------------------------|

| b=fir1(n-1,wp,y);                                  |

| [h,o]=freqz(b,1,256);                              |

| $m=20*\log 10(abs(h));$                            |

| subplot(2,2,1);                                    |

| plot(o/pi,m);                                      |

| ylabel('gain in dB>');                             |

| <pre>xlabel('(a) normalized frequency&gt;');</pre> |

| title('low pass filter');                          |

| %high pass filter                                  |

| b=fir1(n-1,wp,'high',y);                           |

| [h,o]=freqz(b,1,256);                              |

| $m=20*\log 10(abs(h));$                            |

| subplot(2,2,2);                                    |

| plot(o/pi,m);                                      |

| ylabel('gain in dB>');                             |

| <pre>xlabel('(b) normalized frequency&gt;');</pre> |

| title('high pass filter');                         |

|                                                    |

|                                                    |

| %band pass filter                    | %band stop filter                                  |

|--------------------------------------|----------------------------------------------------|

| wn=[wp ws];                          | b=fir1(n-1,wn,'stop',y);                           |

| b=fir1(n-1,wn,y);                    | [h,o]=freqz(b,1,256);                              |

| [h,o]=freqz(b,1,256);                | $m=20*\log 10(abs(h));$                            |

| m=20*log10(abs(h));                  | subplot(2,2,4);                                    |

| subplot(2,2,3);                      | plot(o/pi,m);                                      |

| plot(o/pi,m);                        | ylabel('gain in dB>');                             |

| ylabel('gain in dB>');               | <pre>xlabel('(d) normalized frequency&gt;');</pre> |

| xlabel('(c) normalized frequency>'); | title('stop band filter');                         |

| title('band pass filter');           |                                                    |

|                                      |                                                    |

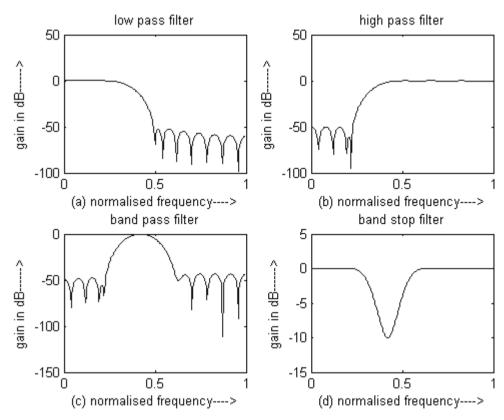

## **MODEL GRAPHS**:

Fig: gain responses of low pass, high pass, band pass and band stop filters

#### Run:

| Enter the pass band ripple    | : 0.03 |

|-------------------------------|--------|

| Enter the stop band ripple    | : 0.02 |

| Enter the stop band frequency | : 2400 |

| Enter the pass band frequency | : 1800 |

| Enter the sampling frequency | : | 10000 |

|------------------------------|---|-------|

| Enter the ripple value in dB | : | 40    |

**RESULT**: Thus the Finite Impulse Response(FIR) of Chebyshev low-pass, high-pass, band pass and band reject filters is simulated in MATLAB.

#### **VIVA Questions:**

- 1. What is the need for a filter?

- 2. What is meant by cut off in filters?

- 3. What is FIR filter?

- 4. What is the transfer function of FIR filter?

#### **Answers:**

- 1. Digital filters that incorporate *digital-signal-processing* (DSP) techniques have received a great deal of attention in technical literature in recent years. Although they rarely serve as anti-aliasing filters (in fact, they need anti-aliasing filters), digital filters merit discussion here because digital filters offer features that have no counterparts in other filter technologies.

- 2. Typically in electronic systems such as filters and communication channels, cutoff frequency applies to an edge in a lowpass, highpass, bandpass, or band-stop characteristic a frequency characterizing a boundary between a passband and a stopband. It is sometimes taken to be the point in the filter response where a transition band and passband meet, for example as defined by a 3 dB corner, a frequency for which the output of the circuit is –3 dB of the nominal passband value. Alternatively, a stopband corner frequency may be specified as a point where a transition band and a stopband meet: a frequency for which the attenuation is larger than the required stopband attenuation, which for example may be 30 dB or 100 dB.

- 3. A **finite impulse response (FIR)** filter is a type of a signal processing filter whose impulse response (or response to any finite length input) is of *finite* duration, because it settles to zero in finite time.

- 4. The transfer function for a linear, time-invariant, digital filter can be expressed as a transfer function in the *Z*-domain; if it is causal, then it has the form:

$$H(z) = \frac{B(z)}{A(z)} = \frac{b_0 + b_1 z^{-1} + b_2 z^{-2} + \dots + b_N z^{-N}}{1 + a_1 z^{-1} + a_2 z^{-2} + \dots + a_M z^{-M}}$$

#### **PROGRAM-7 ECG SIGNAL GENERATION**

25

#### AIM: To design ECG Signal using MATLAB

#### APPARATUS: MATLAB Version 7.8 (R2009a)

#### **PROGRAM**:

#### %PROGRAM for the generation of ECG signal

```

clc:

close all:

else

clear all:

amplitude =');

x = 1:0.01:3;

default = input('press 1 if u want

=');

default ecg signal else 2: ');

if(default ==1)

li = 60/72;

a pwav = 0.25;

d pwav = 0.09;

t pwav = 0.25; %P-R segment

a qwav = 0.1;

d qwav = 0.066;

t qwav = 0.166;

a qrswav = 1.6;

d qrswav = 0.11;

a swav = 0.25;

d swav = 0.066;

t swav = 0.09;

a twav = 0.35;

d twav = 0.142;

t = 0.3;

a uwav = 0.035;

d uwav = 0.0476;

t uwav =0.5;

else

rate = input ('\n enter the heart

beat rate:');

li= 60/rate;

%p wave specifications

fprintf('\n \n pwave

specifications\n');

d = input('enter 1 for default

specification else press 2: ');

if(d == 1)

```

```

d pwav = input('enter duration

t pwav = input('enter p-r

interval =');

d=0;

end

% q wave specifications

fprintf('\n \n q wave

specifications\n');

d = input('enter 1 for default

specification else press 2: ');

if(d == 1)

a qwav = 0.1;

d qwav =0.066;

t^{-}qwav = 0.166;

else

a qwav = input('enter

amplitude');

d qwav = input('enter

duration');

t qwav = input('enter q t

interval');

d = 0;

end

%qrs wave specifications

fprintf('\n \n qrs wave

specifications\n');

d = input('enter 1 for default

specification else press 2: ');

if(d ==1)

a qrswav = 1.6;

d qrswav = 0.11;

else

a qrswav =input('enter

amplitude');

d qrswav =input('enter

duration');

d =0;

end

% s wave specifications

```

a pwav =0.25;

d pwav =0.09;

t pwav =0.25;

a pwav = input('enter

```

fprintf(' \ \ wave

specifications\n');

if(d == 1)

d = input('enter 1 for default

a uwav =0.035;

specification else 2: ');

d uwav =0.0476;

if(d ==1)

t uwav = 0.5;

a swav = 0.25;

else

d swav = 0.066;

a uwav =input('enter

t \, swav = 0.09;

amplitude:');

else

d uwav = input('enter

a swav = input('enter

duration: ');

amplitude');

t uwav = input('enter

d swav = input('enter

interval');

duration');

d=0;

t swav = input ('enter

end

interval');

end

d =0;

% p wave putput

end

pwav =

%t wave specifications

p wav(x,a pwav,d pwav,t pwav,li);

fprintf(' \ \ vave

specifications\n');

% q wave output

d = input('enter 1 for default

qwav = q wav(x -

apecification else 2: ');

if(d ==1)

a twav = 0.35;

d twav =0.142;

grswav =

t twav = 0.3;

else

a twav = input('enter

amplitude');

swav =

d twav = input('enter

duration');

t twav = input('enter s-t

interval');

d=0;

twav =

end

% u wave specifications

fprintf(' \n \n u wave

uwav

specifications\n');

d = input('enter 1 for default

specification else 2: ');

figure;

```

```

0.10, a qwav, d qwav, t qwav, li);

% grs wave output

qrs wav(x,a qrswav,d qrswav,li);

% s wave specifications

s wav(x,a swav,d swav,t swav,li);

% t wave specifications

t wav(x,a twav,d twav,t twav,li);

```

```

% u wave specification

=u wav(x,a uwav,d uwav,t uwav,li);

```

```

%ecq output

ecq = pwav

+qwav+qrswav+swav+twav+uwav;

plot(x,ecg,'r');comet(x,ecg);

title('ECG');grid on;

```

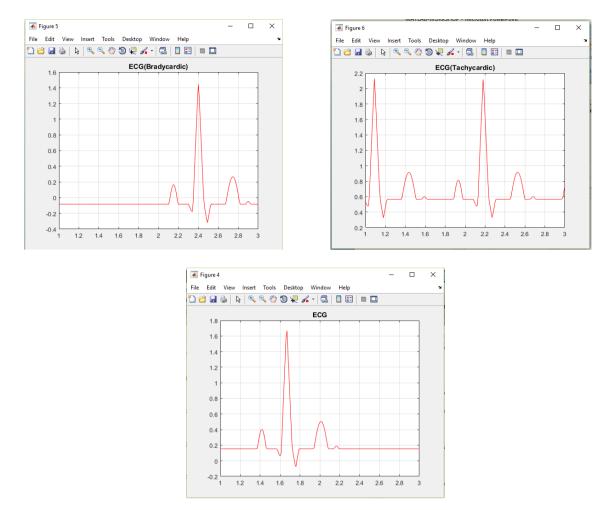

#### **MODEL GRAPHS**:

Fig: ECG signal generation

#### Run:

**RESULT**: Thus the ECG signal is simulated in MATLAB.

**VIVA Questions:**

Answers:

#### **INTRODUCTION TO VHDL**

VHDL is an acronym for VHSIC Hardware Description Language (VHSIC is an acronym for Very High Speed Integrated Circuit). It is a Hardware Description Language that can be used to model a digital system at many levels of abstraction ,ranging from algorithmic level to the gate level. The complexity of the digital system being modeled could vary from that of simple gate to a complex digital electronic system or anything in between. The digital system can also be described hierarchically. Timing can also be explicitly modeled in the same description.

The VHDL language can be regarded as an integrated amalgamation of following languages.

Sequential language + Concurrent language + Net-list language + Timing specifications + Waveform generation language =>VHDL.

The language not only defines the syntax but also defines very clear simulation semantics for each language construct. Therefore models written in this language can be verified using a VHDL simulation.

#### **CAPABILITIES:**

The following are the major capabilities that the language provides along with the features that differentiate it from other hardware description languages.

- The language can be used as an exchange medium between chip vendors and CAD tool users. Different chip vendors can provide VHDL descriptions of their components to system designers. CAD tool users can use it to capture the behavior of the design at a high level of abstraction of functional simulation.

- The language can also be used as a communication medium between different CAD and CAE tools. For example, a schematic capture PROGRAM may be used to generate a VHDL description for the design which can be used as an input to a simulation PROGRAM.

- The language supports hierarchy, that is, a digital system can be modeled as a set of interconnected subcomponents.

- The language supports flexible design methodologies: top-down, bottom-up or mixed.

- It supports both synchronous and asynchronous timing models.

- Various digital modeling techniques, such as finite state machine descriptions, algorithmic descriptions and Boolean equations can be modeled using the language.

- The language supports three basic different description styles: structural, dataflow and behavioral. A design may also be expressed in any combination of these three descriptive styles.

- The language is not technology-specific, but is capable of supporting technology specific features. It can also support various hardware technologies.

#### **BASIC TERMINOLOGY:**

A hardware abstraction of a digital system is called an entity. An entity X when used in another entity Y becomes a component for the entity Y. therefore the component is also an entity, depending on the level at which you are trying to model.

To describe an entity, VHDL provides five different types of primary constructs called design units. They are:

- > Entity declaration.

- Architecture body.

- Configuration declaration.

- Package declaration.

- Package body.

#### • ENTITY DECLARATION:

The entity declaration specifies the name of the entity being modeled and lists the set of interface ports. Ports are signals through which the entity communicates with the other models in its external environment.

#### • ARCHITECTURE BODY:

The internal details of an entity are specified by an architecture body using any of the following modeling styles:

- > As a set of interconnected components (to represent structure).

- ➤ As a set of concurrent assignment statements (to represent dataflow).

- ➤ As a set of sequential assignment statements (to represent behavior).

#### • CONFIGURATION DECLARATION:

This is used to select one of the many possibly architecture bodies that an entity may have, and to bind components, used to represent structure in that architecture body, to entities represented by an entity-architecture pair or by a configuration which reside in a design library.

#### • PACKAGE DECLARATION:

This is used to store a set of common declarations, such as components, types, procedures and functions. These declarations can then be imported into other design units using a 'use' clause.

#### • PACKAGE BODY:

This is used to store the definitions of functions and procedures that were declared in the corresponding package declaration, and also complete constant declarations for any deferred constants that appear in the package in the package declaration.

#### STRUCTURAL MODELING:

In the structural style of modeling, an entity is described as a set of interconnected components. Example: Half adder. The entity declaration for half adder specifies the interface ports for this architecture body. The architecture body is composed of two parts: the declarative part (before the keyword **begin**) and the statement part(after the keyword **begin**). Two component declarations are present in the declarative part of the architecture body. These declarations specify the interface of components that are used in the architecture body. The declared components are instantiated in the statement part of the architecture body using component labels for these component instantiation statements. The signals in the port map of a component instantiated and the port signals in the component declaration are associated by position (called positional association). However the structural representation for the Half adder does not say anything about its functionality. Separate entity models would be described for the components XOR2 and AND2, each having its own entity declaration and architecture body.

A component instantiated statement is a concurrent statement. Therefore, the order of these statements is not important. The structural style of modeling describes only an interconnection of components, without implying any behavior of the components themselves nor the entity that they collectively represent.

30

#### **DATAFLOW MODELING:**

In this modeling style, the flow of data through the entity is expressed primarily using concurrent signal assignment statements. The structure entity of the entity is not explicitly specified in this modeling style, but it can be implicitly deduced. In a signal assignment statement, the symbol <= implies an assignment of a value to a signal. The value of the expression on the right-hand-side of the statement is computed and is assigned to the signal on the left-hand-side, called the target signal. A concurrent signal assignment statement is executed only when any signal used in the expression on the right-hand-side has an event on it, that is, the value for the signal changes.

#### **BEHAVIORAL MODELING:**

The behavioral modeling specifies the behavior of an entity as a set of statements that are executed sequentially in the specified order. This set of sequential statements, which are specified inside a process statement, do not explicitly specify the structure of the entity but merely its functionality. A process statement is a concurrent statement that can appear within an architecture body. A process statement also has a declarative part (before the keyword **begin**) and a statement part (between the keywords **begin** and **end process**). The statements appearing within the statement part are sequential statements and are executed sequentially. The list of signals specified within the parenthesis after the keyword **process** constitutes a sensitivity list, and the process statement is invoked whenever there is an event on any signal in this list.

A variable is assigned using the assignment operator := compound symbol; contrast this with a signal that is assigned a value using the assignment operator <= compound symbol. Signal assignment statements appearing within a process are called sequential signal assignment statements. Sequential signal statements, including variable assignment statements, are executed sequentially independent of whether an event occurs on any signals in its right-hand-side expression; contrast this with the execution of concurrent signal assignment statements in the dataflow modeling style.

31

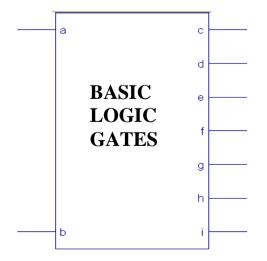

#### PROGRAM -1 LOGIC GATES

AIM: - To write a PROGRAM in VHDL for simulating the basic gates- AND, OR, OT, NAND,

NOR, XOR, XNOR and to verify its functionality.

APPARATUS: Model Sim 5.7

## PROGRAM:-

| library ieee;                             | d<= a or b;                    |

|-------------------------------------------|--------------------------------|

| use ieee.std_logic_1164.all;              | e<= not b;                     |

| entity logicgates is                      | f<= a xor b;                   |

| port(a,b: in std_logic;c,d,e,f,g,h,i: out | g<= a nand b;                  |

| std_logic);                               | $h \le not(a \text{ xor } b);$ |

| end logicgates;                           | i<= a nor b;                   |

| architecture dataflow of logicgates is    | end dataflow;                  |

| begin                                     |                                |

| $c \le a \text{ and } b;$                 |                                |

|                                           |                                |

## TRUTH TABLE:-

| INP | UTS | OUTPUTS |    |     |     |      |      |     |  |  |

|-----|-----|---------|----|-----|-----|------|------|-----|--|--|

| а   | h   | AND     | OR | NOT | XOR | NAND | XNOR | NOR |  |  |

| u   | U   | с       | d  | e   | f   | g    | h    | i   |  |  |

| 0   | 0   | 0       | 0  | 1   | 0   | 1    | 1    | 1   |  |  |

| 0   | 1   | 0       | 1  | 0   | 1   | 1    | 0    | 0   |  |  |

| 1   | 0   | 0       | 1  | 1   | 1   | 1    | 0    | 0   |  |  |

| 1   | 1   | 1       | 1  | 0   | 0   | 0    | 1    | 0   |  |  |

## **RTL SCHEMATIC:**

#### **WAVEFORMS:**

| <b></b> v | vave | e - def                                                                          | ault                                                             |                            |      |                            |       |     |      |   |    |      |             |     |          |   |    |    |    |   |

|-----------|------|----------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------|------|----------------------------|-------|-----|------|---|----|------|-------------|-----|----------|---|----|----|----|---|

| File      | Edi  | t View                                                                           | Ins                                                              | ert                        | Form | nat                        | Tools | Wir | ndow | V |    |      |             |     |          |   |    |    |    |   |

| <b>2</b>  |      | 8                                                                                | <mark>Ж</mark> ∣                                                 | <b>B</b>                   | 6    | řů,                        | ₽.    | X   | t    | ₹ | ٩, | ]  ( | <b>Q</b> (6 | ۵ 🔍 | <b>.</b> | Ŧ | ₹Ļ | ₹¢ | ī₽ | X |

|           |      | /logicg.<br>/logicg.<br>/logicg.<br>/logicg.<br>/logicg.<br>/logicg.<br>/logicg. | ates/b<br>ates/c<br>ates/c<br>ates/e<br>ates/f<br>ates/ <u>c</u> | )<br>;<br>;<br>;<br>;<br>; |      | 0<br>1<br>0<br>1<br>0<br>0 |       |     |      |   |    |      |             |     |          |   |    |    |    |   |

**RESULT**: - Hence all the logic gates are simulated in VHDL using dataflow modeling and their functionality is verified.

#### **VIVA QUESTIONS:**

- 1. What is VHDL?

- 2. What is the need for VHDL?

- 3. What is meant by simulation?

- 4. What is meant by synthesis?

- 5. Who initialized the VHDL and in which year?

#### **ANSWERS:**

- 1. It is acronym for <u>Very high-speed digital integrated circuit Hardware</u> <u>Descriptive Language</u>.

- 2. VHDL is needed to synthesize circuits with millions of gates.

- 3. It is a software program that tests the functionality and timing of a circuit to be designed.

- 4. A translation from a higher level of abstraction to a lower level is synthesis.

- 5. United States Department of Defense(DoD) in the year 1980.

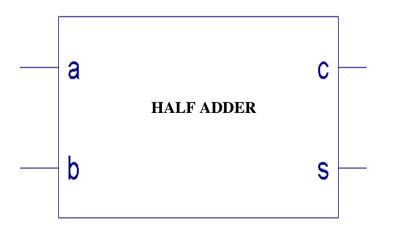

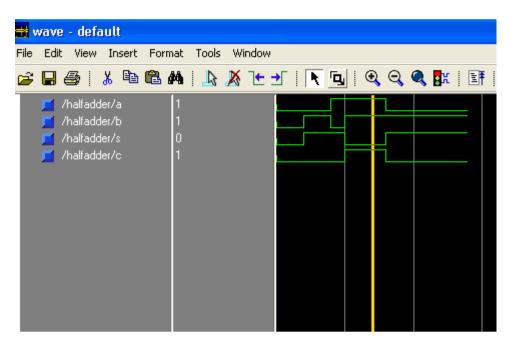

## PROGRAM 2(a) HALFADDER

**AIM:** - To write a PROGRAM in VHDL for simulating the half adder and to verify its functionality.

## APPARATUS: Model Sim 5.7

## PROGRAM:-

| library ieee;                                           | architecture dataflow of halfadder is |

|---------------------------------------------------------|---------------------------------------|

| use ieee.std_logic_1164.all;                            | begin                                 |

| entity halfadder is                                     | s<= a xor b;                          |

| <pre>port(a,b: in std_logic; s,c: out std_logic);</pre> | $c \le a$ and b;                      |

| end halfadder;                                          | end dataflow;                         |

|                                                         |                                       |

## TRUTH TABLE:-

| INP | UTS | OUTPUTS  |            |  |  |

|-----|-----|----------|------------|--|--|

| a   | b   | Sum<br>s | Carry<br>c |  |  |

| 0   | 0   | 0        | 0          |  |  |

| 0   | 1   | 1        | 0          |  |  |

| 1   | 0   | 1        | 0          |  |  |

| 1   | 1   | 0        | 1          |  |  |

## **RTL SCHEMATIC:**

## **WAVEFORMS:**

**RESULT**:- Hence the half adder is simulated in VHDL using data flow modeling and its functionality is verified.

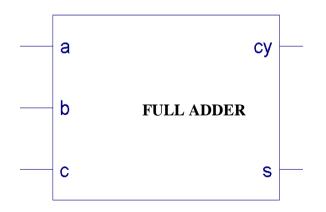

## PROGRAM 2(b) FULL ADDER

AIM: - To write a PROGRAM in VHDL for simulating the full adder and to verify

its functionality.

## APPARATUS: Model Sim 5.7

## PROGRAM:-

| aflow of fulladder is      |

|----------------------------|

|                            |

| r c;                       |

| or (b and c) or (c and a); |

|                            |

| 1                          |

## TRUTH TABLE:-

|   | INPUT | OUTPUTS |   |    |  |

|---|-------|---------|---|----|--|

| a | b     | с       | S | cy |  |

| 0 | 0     | 0       | 0 | 0  |  |

| 0 | 0     | 1       | 1 | 0  |  |

| 0 | 1     | 0       | 1 | 0  |  |

| 0 | 1     | 1       | 0 | 1  |  |

| 1 | 0     | 0       | 1 | 0  |  |

| 1 | 0     | 1       | 0 | 1  |  |

| 1 | 1     | 0       | 0 | 1  |  |

| 1 | 1     | 1       | 1 | 1  |  |

## **RTL SCHEMATIC:**

| 🕂 wave - default                                                                                                          |                                                 |

|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| File Edit View Insert Fo                                                                                                  | ormat Tools Window                              |

| 😅 日 🎒   👗 🖻 🛍                                                                                                             | 1 M   <u>}</u> 🔆 🛨   💽 🖳 🔍 🔍 🔍 👫   Ef   El El E |

| <ul> <li>/fulladder/a</li> <li>/fulladder/b</li> <li>/fulladder/c</li> <li>/fulladder/s</li> <li>/fulladder/cy</li> </ul> |                                                 |

**RESULT**: - Hence the full adder is simulated in VHDL and its functionality is verified.

#### **VIVA QUESTIONS:**

- 1. What is the assignment operator for i) signal ii) variable ?

- 2. What is the difference between signal and a variable?

- 3. Is process used for combinational or sequential logic?

- 4. What is the difference between function and procedure?

- 5. Define i) entity ii) architecture.

#### **ANSWERS:**

- 1. '<=' and ':='.

- Nonstatic values can be passed in VHDL by two ways: signals and variables.

A signal can be declared in package, entity or architecture, while a variable can be declared within a piece of sequential code. The value of former can be global and the later can be local.

- 3. Process can imply combinational or sequential logic, depending upon how it is used.

- 4. Function can return only one value, whereas procedure can return any no. of values.

- 5. The entity declaration describes the input and output of the design. It describes the external interface to the design.

Architecture describes the internal implementation of the design. The architecture body describes the internal working of the entity and contains any combination of structural, dataflow, or behavioral descriptions used to describe the internal working of the entity.

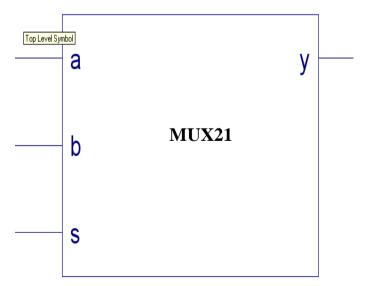

# PROGRAM 3(a) 2x1 Multiplexer

**AIM:**- To write a code in VHDL for simulating the 2x1 multiplexer and to verify its functionality. **APPARATUS**: Model Sim 5.7

# PROGRAM:-

| library ieee;                                           | begin                |

|---------------------------------------------------------|----------------------|

| use ieee.std_logic_1164.all;                            | case s is            |

| entity mux21 is                                         | when '0'=>y<=a;      |

| <pre>port(a,b:in std_logic; s:in std_logic; y:out</pre> | when '1'=>y<=b;      |

| std_logic);                                             | when others=>y<='U'; |

| end mux21;                                              | end case;            |

| architecture beh of mux21 is                            | end process;         |

| begin                                                   | end beh;             |

| process(a,b,s)                                          |                      |

# TRUTH TABLE:-

| SELECT<br>INPUT | OUTPUT |

|-----------------|--------|

| S               | Y      |

| 0               | а      |

| 1               | b      |

# **RTL SCHEMATIC:**

| wave - default                                                                     |                  |         |           |           |

|------------------------------------------------------------------------------------|------------------|---------|-----------|-----------|

| Edit View Insert Forn                                                              | nat Tools Window |         |           |           |

| j 🖬 🍜 🌋 🗍 🕺 🖻                                                                      | ) 🛍 🖊 📙 🕹 🤰      | § 飞 → ] | <br>1419- | 54 MM 🕅 I |

| f   14 14 14 14                                                                    |                  |         |           |           |

| <ul> <li>/mux21/a</li> <li>/mux21/b</li> <li>/mux21/s</li> <li>/mux21/y</li> </ul> | 0<br>1<br>0<br>0 |         |           |           |

**RESULT**:- Hence the 2x1 multiplexer is simulated in VHDL and its functionality is verified.

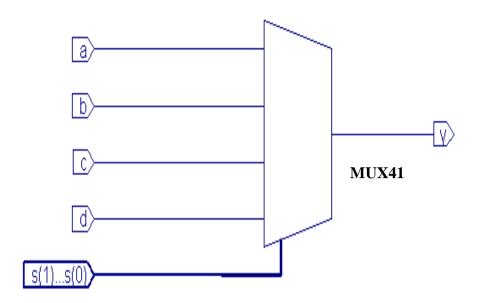

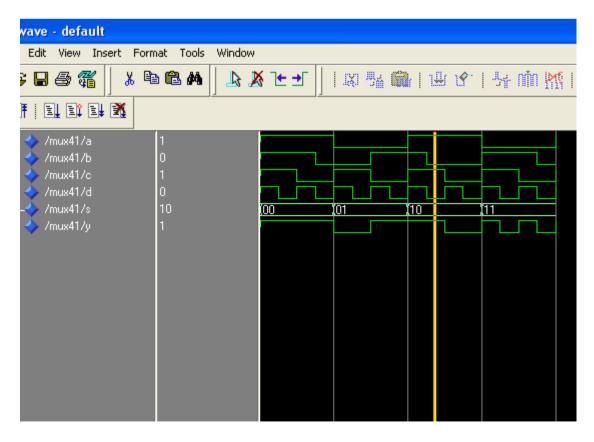

# PROGRAM 3(b) 4x1 Multiplexer

AIM:- To write a code in VHDL for simulating the 4x1 multiplexer and to observe the waveforms.APPARATUS: Model Sim 5.7PROGRAM:-

| when "00"=>y<=a;     |

|----------------------|

| when "01"=>y<=b;     |

| when "10"=>y<=c;     |

| when "11"=>y<=d;     |

| when others=>y<='U'; |

| end case;            |

| end process;         |

| end beh;             |

|                      |

|                      |

|                      |

|                      |

|                      |

# **TRUTH TABLE:-**

| SELECT |           | OUTPUTS |

|--------|-----------|---------|

| DATA   |           |         |

| INPUTS |           |         |

| S1     | <b>S0</b> | Y       |

| 0      | 0         | D0      |

| 0      | 1         | D1      |

| 1      | 0         | D2      |

| 1      | 1         | D3      |

#### **RTL SCHEMATIC:**

#### **WAVEFORMS:**

**RESULT**:- Hence the 4x1 multiplexer is simulated in VHDL and its functionality is verified.

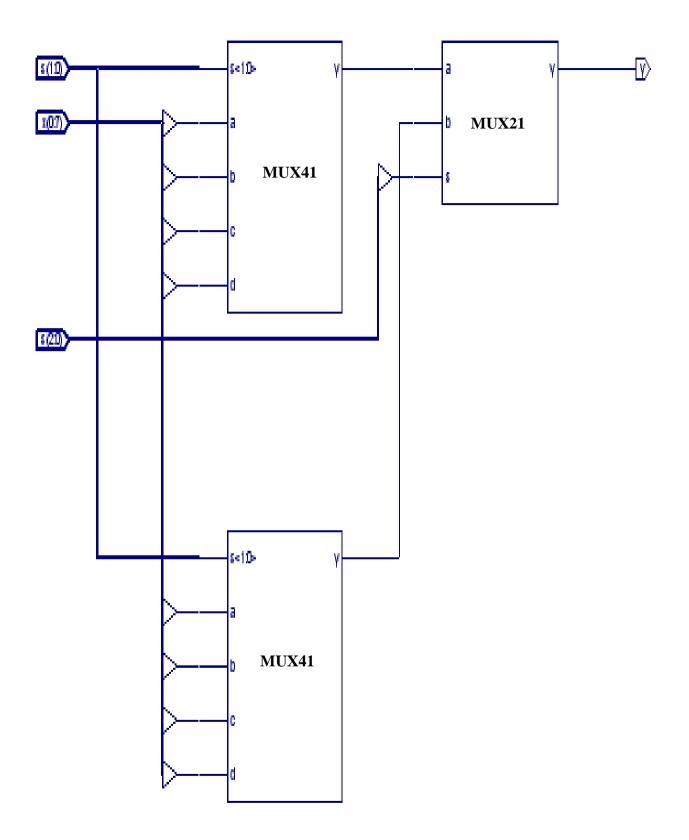

# PROGRAM 3(c) 8x1 Multiplexer

**AIM:-** To write a code in VHDL for simulating the 8x1 multiplexer and to verify its functionality.

APPARATUS: Model Sim 5.7

# PROGRAM:-

| library ieee;                                                 | component mux21                                        |

|---------------------------------------------------------------|--------------------------------------------------------|

| use ieee.std_logic_1164.all;                                  | <pre>port(a,b,s: in std_logic;y: out std_logic);</pre> |

| entity mux81 is                                               | end component;                                         |

| <pre>port(x:in std_logic_vector(0 to 7);s:in</pre>            | signal p1,p2: std_logic;                               |

| <pre>std_logic_vector(2 downto 0);y:out std_logic);</pre>     | begin                                                  |

| end mux81;                                                    | X1: mux41 port map(x(0),x(1),x(2),x(3),s(1             |

| architecture structure of mux81 is                            | downto 0),p1);                                         |

| component mux41                                               | X2: mux41 port map(x(4),x(5),x(6),x(7),s(1             |

| <pre>port(a,b,c,d:in std_logic;s: in std_logic_vector(1</pre> | downto 0),p2);                                         |

| downto 0);y: out std_logic);                                  | X3: mux21 port map(p1,p2,s(2),y);                      |

| end component;                                                | end structure;                                         |

|                                                               |                                                        |

| wave - default                         |             |                                |           |                 |             |  |  |  |

|----------------------------------------|-------------|--------------------------------|-----------|-----------------|-------------|--|--|--|

| Edit View Insert Format Tools Window   |             |                                |           |                 |             |  |  |  |

| ≩ 🖬 🚑 🎇 🗍 🔏 🗎                          | ) 🛍 🗛 🗍 💄 🌶 | § Ҽ ➔ 🗍 !                      | IXI 👫 儱   | 1 <u>11</u> 18. | - 👬 nằn 👯 I |  |  |  |

| it i i i i i i i i i i i i i i i i i i |             |                                |           |                 |             |  |  |  |

| -                                      | 0100000     | <u>10000000</u><br>000 00<br>- | <u>01</u> |                 | 010         |  |  |  |

**RESULT**:- Hence the 8x1 multiplexer is simulated in VHDL using structural modeling and its functionality is verified.

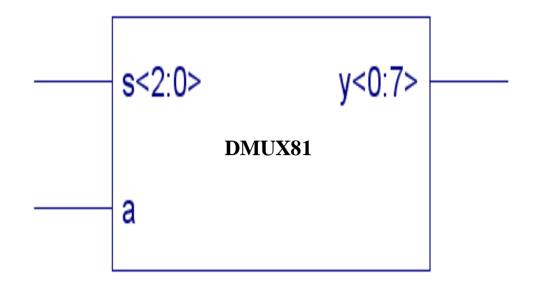

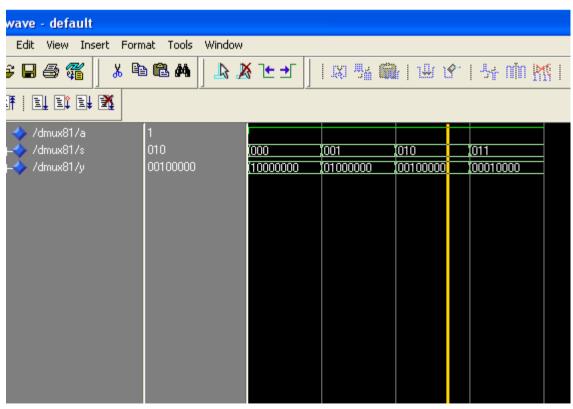

# PROGRAM 3(d) 1x8 Demultiplexer

**AIM:-** To write a code in VHDL for simulating the 8x1 demultiplexer and to verify its functionality.

# APPARATUS: Model Sim 5.7

### PROGRAM:-

| Library ieee;                                            | when "000"=>y(0)<=a;        |

|----------------------------------------------------------|-----------------------------|

| use ieee.std_logic_1164.all;                             | when "001"=>y(1)<=a;        |

| entity dmux81 is                                         | when "010"=>y(2)<=a;        |

| <pre>port(a: in std_logic;s: in std_logic_vector(2</pre> | when "011"=>y(3)<=a;        |

| <pre>downto 0);y: out std_logic_vector(0 to 7));</pre>   | when "100"=>y(4)<=a;        |

| end dmux81;                                              | when "101"=>y(5)<=a;        |

| architecture dmux of dmux81 is                           | when "110"=>y(6)<=a;        |

| begin                                                    | when "111"=>y(7)<=a;        |

| process(a,s)                                             | when others=>y<="UUUUUUUU"; |

| begin                                                    | end case;                   |

| y<="00000000";                                           | end process;                |

| case s is                                                | end dmux;                   |

#### **TRUTH TABLE:-**

| DATA<br>INPUT |    | SELEC      |            | OUTPUTS |    |    |    |    |    |    |    |

|---------------|----|------------|------------|---------|----|----|----|----|----|----|----|

| a             | S2 | <b>S</b> 1 | <b>S</b> 0 | Y0      | Y1 | Y2 | Y3 | Y4 | Y5 | Y6 | Y7 |

| a             | 0  | 0          | 0          | а       | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| a             | 0  | 0          | 1          | 0       | a  | 0  | 0  | 0  | 0  | 0  | 0  |

| a             | 0  | 1          | 0          | 0       | 0  | a  | 0  | 0  | 0  | 0  | 0  |

| а             | 0  | 1          | 1          | 0       | 0  | 0  | a  | 0  | 0  | 0  | 0  |

| a             | 1  | 0          | 0          | 0       | 0  | 0  | 0  | a  | 0  | 0  | 0  |

| а             | 1  | 0          | 1          | 0       | 0  | 0  | 0  | 0  | a  | 0  | 0  |

| а             | 1  | 1          | 0          | 0       | 0  | 0  | 0  | 0  | 0  | a  | 0  |

| а             | 1  | 1          | 1          | 0       | 0  | 0  | 0  | 0  | 0  | 0  | а  |

### **RTL SCHEMATIC:**

#### **WAVEFORMS:**

**RESULT**:- Hence the 1x8 demultiplexer is simulated in VHDL using behavioral modeling and its functionality is verified.

#### **VIVA QUESTIONS:**

- 1. What are the basic sections of a VHDL code?

- 2. Define i) STD\_LOGIC\_1164 ii) STD\_LOGIC\_ARITH iii) STD\_LOGIC\_UNSIGNED

- 3. What are the rules to be followed while specifying data object names?

- 4. What are the values the data type STD\_LOGIC can assume?

- 5. How the value of individual SIGNAL and multibit SIGNAL are specified?

#### **ANSWERS:**

- 1. Library, entity and architecture.

- i) defines the standard for describing the interconnection ii) defines UNSIGNED and SIGNED types, conversion iii) defines functions to allow the use of STD\_LOGIC\_VECTOR types as if they were UNSIGNED types

- 3. Any alphanumeric character may be used in the name, as well as the '\_'underscore character. A name cannot be a VHDL keyword, it must begin with a letter, it cannot end with an '\_' underscore, and it cannot have two successive underscores.

- 4. 'U' -- Unintaialized

- 'X' -- Forcing unknown

- '0' -- Forcing 0

- '1'-- Forcing 1

- 'Z' -- High impedance

- 'W' -- Weak unknown

- ' L' -- Weak 0

- 'H' --Weak 1

- '- ' --Don't care

- 5. The value of an individual SIGNAL is specified using apostrophes, as in '0' or '1'. The value of a multibit SIGNAL is given with double quotes.

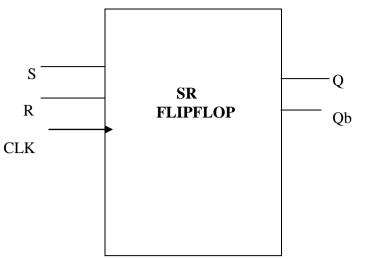

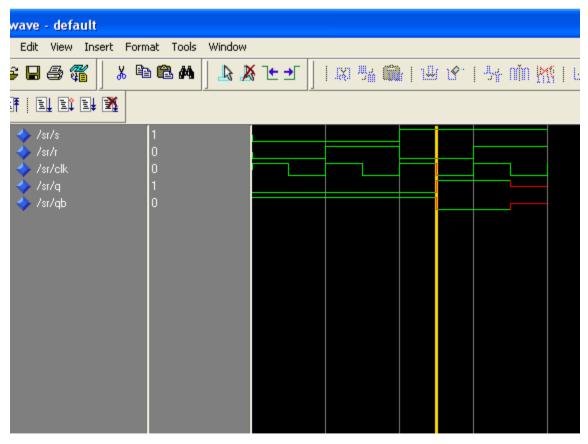

# PROGRAM 4(a) SR FLIP FLOP

**AIM:**- To write a code in VHDL for simulating the SR flip-flop and to verify its functionality. **APPARATUS**: Model Sim 5.7

#### PROGRAM:-

| library ieee;                                       | tb:=Qb;                                    |

|-----------------------------------------------------|--------------------------------------------|

| use ieee.std_logic_1164.all;                        | if (clk='0'and clk'event) then             |

| entity SR is                                        | if(S='0'and R='0') then t:=t;tb:=tb;       |

| <pre>port(S,R,clk: in std_logic;Q:inout</pre>       | elsif(S='0'and R='1') then t:='0';tb:='1'; |

| <pre>std_logic:='0';Qb:inout std_logic:='1');</pre> | elsif(S='1'and R='0') then t:='1';tb:='0'; |

| end SR;                                             | elsif(S='1'and R='1') then t:='U';tb:='U'; |

| architecture ff of SR is                            | end if;                                    |

| begin                                               | Q<=t;                                      |

| process(S,R,clk)                                    | Qb<=tb;                                    |

| variable t,tb: std_logic;                           | end if;                                    |

| begin                                               | end process;                               |

| t:=Q;                                               | end ff;                                    |

# **TRUTH TABLE:-**

| INPUTS |   | OUTPUTS |    |

|--------|---|---------|----|

| S      | R | Q       | Qb |

| 0      | 0 | Q       | Qb |

| 0      | 1 | 0       | 1  |

| 1      | 0 | 1       | 0  |

| 1      | 1 | Х       | Х  |

#### **RTL SCHEMATIC:**

#### **WAVEFORMS:**

**RESULT**:- Hence the SR flip-flop is simulated in VHDL and its functionality is verified.

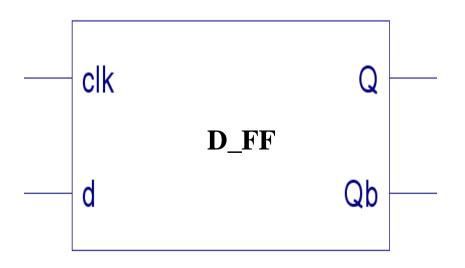

# PROGRAM 4(b) D Flip-Flop

**AIM:-** To write a code in VHDL for simulating the D flip-flop and to verify its functionality. **APPARATUS**: Model Sim 5.7

#### PROGRAM:-

| begin                          |

|--------------------------------|

| if (clk='0' and clk'event)then |

| q<=d;                          |

| qb<=not(d);                    |

| end if;                        |

| end process;                   |

| end behaviour;                 |

|                                |

|                                |

|                                |

| q<br>q<br>e                    |

### **TRUTH TABLE:-**

| INPUTS | OUTPUTS |    |  |

|--------|---------|----|--|

| D      | Q       | Qb |  |

| 0      | 0       | 1  |  |

| 1      | 1       | 0  |  |

### **RTL SCHEMATIC:**

| wave - default                                                                            |                   |                 |                  |

|-------------------------------------------------------------------------------------------|-------------------|-----------------|------------------|

| Edit View Insert Form                                                                     | nat Tools Window  |                 |                  |

| ; 🖬 🗇 🌋 🗍 🕺 🖻                                                                             | a 🛍 🖊 📙 🔈 🗶 🗶 🛨 🛨 | IXI 👫 🏫   III 1 | 🕙   ማቶ በሽስ 🕅 I P |

|                                                                                           |                   |                 |                  |

| <ul> <li>✓ /d_ff/d</li> <li>✓ /d_ff/clk</li> <li>✓ /d_ff/q</li> <li>✓ /d_ff/qb</li> </ul> |                   |                 |                  |

|                                                                                           |                   |                 |                  |

**RESULT**:- Hence the D flip-flop is simulated in VHDL and its functionality is verified. **VIVA QUESTIONS**:

- 1. What are the various types of operators supported by VHDL?

- 2. What are the different concurrent assignment statements?

- 3. What are the different sequential assignment statements?

- 4. What is the purpose of PROCESS statement?

- 5. Give the general form of CASE statement.

#### **ANSWERS:**

1. Boolean(AND, OR,NAND, NOR,XOR, XNOR), arithmetic(\*,/.MOD,REM,-,&), and relational(=,/<,<=,>,>=)

2. Simple signal assignment, selected signal assignment, conditional signal assignment, and generate statements.

3. IF statement, CASE statement, and two types of Loop statement(FOR-LOOP and WHILE-LOOP)

4. To separate the sequential statements from concurrent statements, PROCESS statement is used. The PROCESS statement appears inside an architecture body, and it encloses other statements

within it. The IF, CASE, and LOOP statements can appear only inside a process.

# 5. CASE expression IS

WHEN constant\_value =>

statement;

{statement;}

WHEN constant\_value =>

statement;

{statement;}

#### WHEN OTHERS =>

statement;

{statement;}

END CASE;

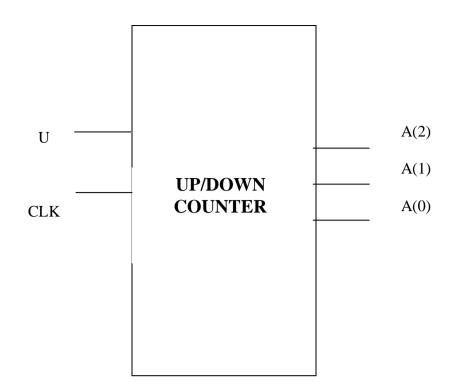

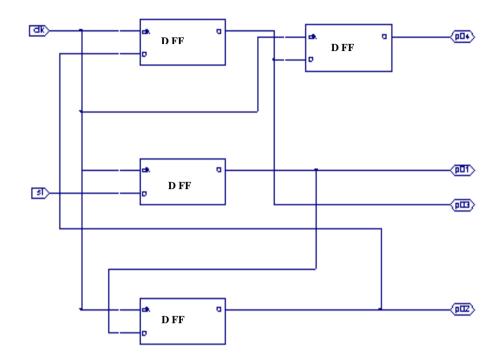

# PROGRAM 5(a) Up-Down Counter

**AIM:-** To write a code in VHDL for simulating the three bit up/down counter using behavioral model and to verify its functionality.

APPARATUS: Model Sim 5.7

# PROGRAM:-

| library ieee;                                    | process(clk,a,u)                |

|--------------------------------------------------|---------------------------------|

| use ieee.std_logic_1164.all;                     | begin                           |

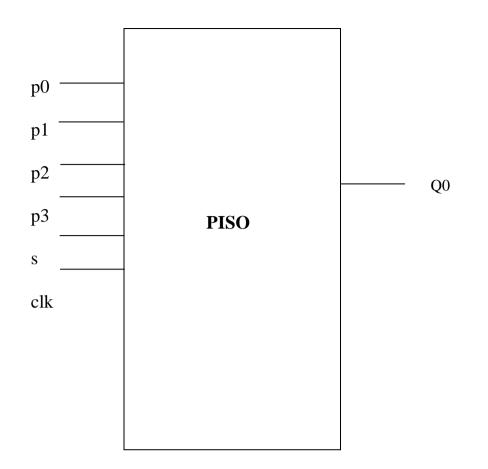

| use ieee.std_logic_arith.all;                    | if (clk='0' and clk'event) then |